* Klicken Sie hier um auf die nächste Seite zu kommen.

INSIGNIS Technology Corporation

Abstract

As semiconductor manufacturing runs headlong into economic and technical challenges, the markets that can afford to amortize the costs and assume the risks of bleeding edge technologies become smaller. At some point the entire industry will bifurcate into a legacy and specialty market - one that is able to cross the chasm into new memory devices and architectures. DDR4 may look like a commodity now, but once the remaining 3 DRAM technology developers move on to the next big thing, there is no licensee or foundry able to support advanced DDR4 in a competitive marketplace. Consider legacy DRAM supported by secondary and fab-less DRAM makers today with devices selling at a price 2x to 5x their historic lows, and then consider a specialty device like RLDRAM selling for a 5x higher premium. DRAM makers have been waiting for sufficient market consolidation to be able to finally raise their profit margins to CPU manufacturer levels. That time will be here sooner than you can imagine.

Introduction

Industrial applications are designed to perform a specific function in a reliable manner and in harsh environments, and the performance requirement is fixed for the life of a product. It is true that a newer, replacement system for a RT application may be higher performance, but for one that is in service in the field, that is not the case. Most embedded applications do not benefit from the rapid advancement of system performance by moving to the newest processors and memory technology. They continue to ship legacy CPUs and controllers from well-established suppliers and require long term support for the peripheral components such as memories.

Moving these applications to advanced semiconductor fabrication processes and faster device designs can prove to be problematic. The newer devices can be more susceptible to minor perturbations from system circuit noise and similar disturbances from high energy particles or cosmic radiation due to increased voltage regulation, lower core voltage, and faster edge rates. Some of the observed failure mechanisms can be designed-out or worked-around in new memory controllers or implementations, but systems already in the field don’t have that option. Memories used in applications designed years ago with now mature controllers need memory that meets the reliability and quality expectations of the original design.

The major, high volume memory suppliers will continue to support legacy functionality by migrating devices to a more advanced process node, but will only do so if it continues to make economic sense. They will promise to support indefinitely until the day it is determined to be the end of the line for a product, and then the dreaded last time buy appears without warning. Most astute customers recognize the peril this places them in and will migrate to alternative long term suppliers well in advance so the customer can establish run rates and favorable terms for extended support. In addition to the obvious business advantages, there are technical reasons to avoid die shrinks.

DRAM design and fabrication

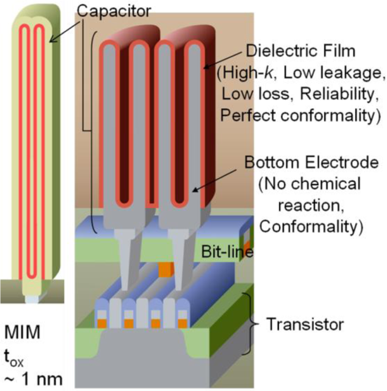

A DRAM stores data on a capacitor that is isolated by a ‘pass’ transistor. This combination is referred to as the bit cell with each one having x and y dimensions of a few tens of nanometers. The capacitor is fabricated in the space above the circuitry, and in modern DRAM bit cells, the capacitor resembles a tall, thin-wall cylinder, with the dielectric on both the inside and outside surfaces of the tube. As the process geometry shrinks, it becomes easier than ever to upset the value on a bit cell either by disturbing the capacitor, the pass transistor, or the bit-line which connects to the sense circuitry. The sense operation measures millivolts of differences caused by a small capacitor driving a large bitline. The bitline is connected to hundreds of pass transistors and the parasitic capacitance of the bitline itself can be more than 10x larger that the bit cell capacitor.

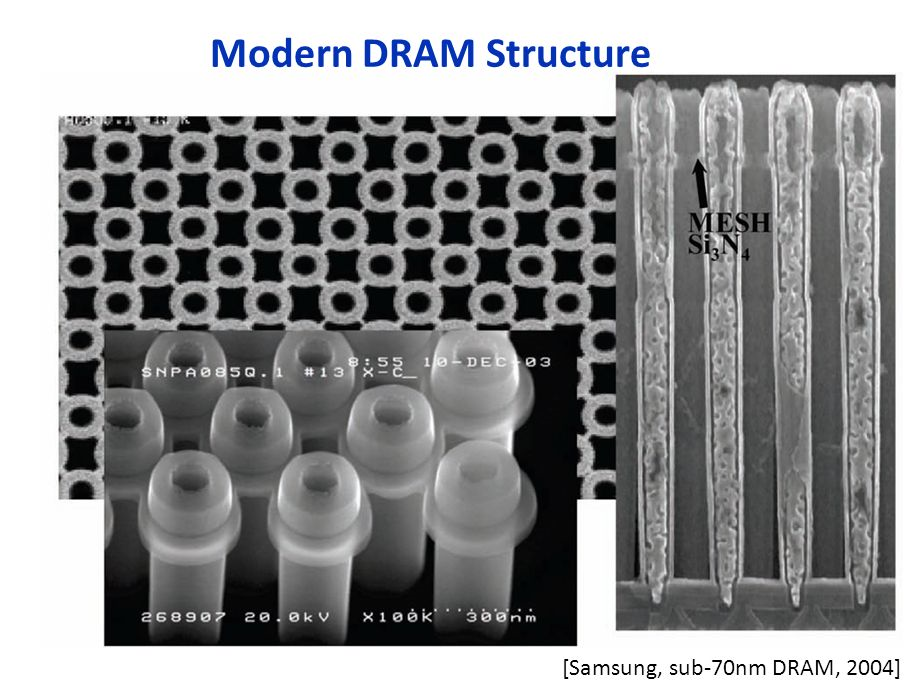

The diagram to the right doesn’t do justice to the complexity of the DRAM capacitor array. The capacitors are so tall they need to be mechanically stabilized with a mesh so the spacing between them doesn’t vary, otherwise the charge of one capacitor can corrupt an adjacent one. Below is an image from 2004 where the capacitors are short and stubby compared to current device technology, and includes a silicon nitride mesh which stabilizes the location of the capacitor during device fabrication. Without the mesh, the capacitors would lean over and contact adjacent cells.